ASUS ROG Rampage Formula: Why we were wrong about the Intel X48

by Kris Boughton on January 25, 2008 4:30 AM EST- Posted in

- Motherboards

The Rules of Working with tRD: What's Allowed and What Isn't

We mentioned earlier that there are a few rules pertaining to the modification of the default tRD value for a particular memory subsystem configuration. These rules are actually more of a set of equations that we have derived in order to assist the user in pre-determining whether or not a system will POST and operate given the settings in question. They can also be used to explain after the fact why certain configurations refuse to function.

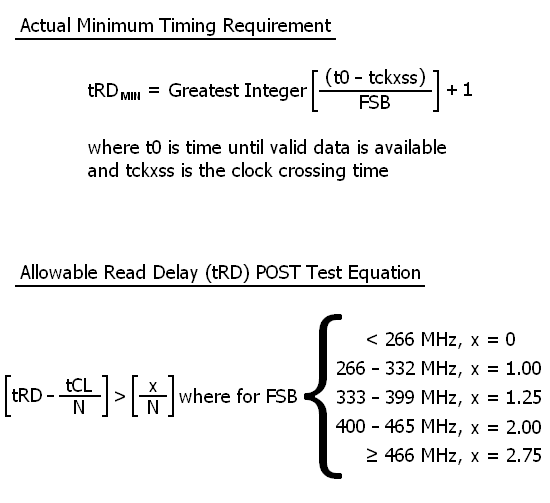

In actuality, there is only one requirement that must be satisfied when setting tRD: The MCH must have a minimum amount of time to complete the clock crossing procedure for each data bit translated from one clocking domain to the other. We have shown the equation below for those that care to know. Unfortunately it does not lend itself well to being solved as the input variables ("t0" and "tckxss") are not readily obtainable.

"t0" is the total time it takes data being returned to the CPU as read in memory to cross from the memory bus domain to the system data bus domain. This is dependent on a number of variables, including memory burst length (4 or 8 cycles), Command Rate (1N or 2N), the memory divider in use, CAS (tCL) timing, and the current FSB. "tckxss" is a little more esoteric in nature and is outside the scope of this discussion; the value is generally very small when compared to "t0". The difference in these times, rounded to the lowest integer plus one, bounds the lowest potential tRD setting necessary for data to be properly transferred from one bus to the other.

Because the first expression is too difficult to warrant everyday use, we spent many hours populating a large test matrix table created for recording the POST (Power On Self Test) results of every strap/divider/FSB/CAS setting combination that our test bench was physically capable of supporting. Using this data, we then developed the method and equation you see above, which can determine whether or not a desired memory subsystem configuration will work. It is possible, and rather probable, that there is another step discontinuity in the logic for FSB speeds in excess of the high value in our test range (466MHz). We will leave the discovery of some such value up to others - unless Intel is kind enough to send us additional 45nm dual-core processors, in which case further testing on our part might be justified.

Entering arguments for the use of the "POST Test Equation" are as follows: tRD, in clocks; tCL (CAS), in clocks; FSB, in megahertz (MHz); N, the memory divider in use, expressed in fractional form (i.e. 3:2 would be 3/2); and "x", which should be chosen from the options provided, depending on the FSB in use. Evaluate the left and right side of the equation separately. The expression is satisfied if the left (actual margin) is greater than but not equal to the right (the minimum required margin).

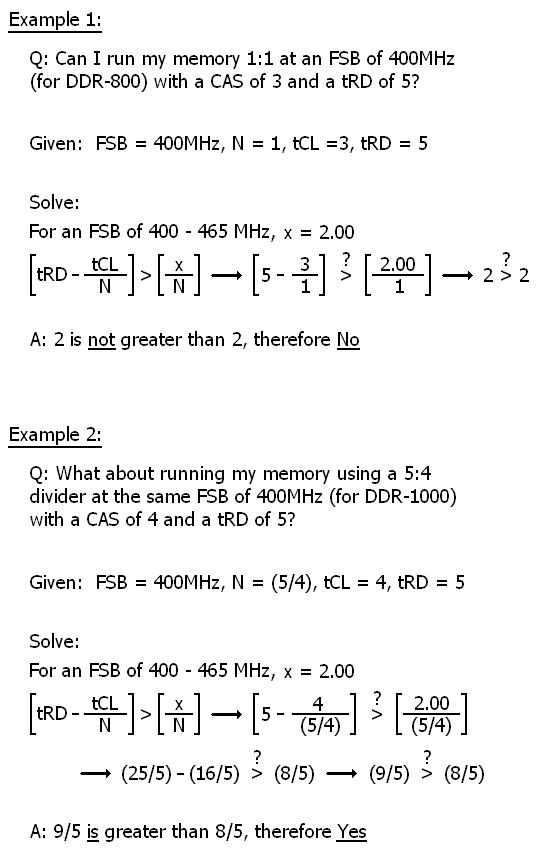

There are no units purposefully associated with these numbers, as this equation is intended as nothing more than a test to determine whether a system will POST using the desired parameters. If the expression is false, the configuration/system will fail to boot; if it is true then the configuration is allowed and the POST event should at least occur. Keep in mind that this equation provides absolutely no assurance that the system will be stable at the settings provided - just because you want to run your memory at DDR2-1200 CAS 3 and the equation says this is possible, does not mean that your wish will be fulfilled. Let's go through a quick exercise of what we have learned regarding the proper use of the "POST Test Equation" with a few practical examples.

If you can follow these examples then you are ready to move on to the next step - determining optimal system performance points and then validating your results. There are many choices when it comes to deciding how to configure a system for the best possible experience. Some choices are clearly better while other decisions may come to down to personal preference. For instance, some users may be willing to subject their expensive hardware components to higher voltages, creating an environment of accelerated wear and earlier failure. Others may be far less concerned with the consequences of their choices; in either case the trade-offs will be clear. We will now take what we have learned and provide our rationale for why we would feel one overclocking approach to be superior to another. After all, overclocking should always be based on an intelligent decision making process and not the clumsy application of brute-force.

73 Comments

View All Comments

Vikendios - Thursday, January 31, 2008 - link

Very Interesting. But I believe that AT is also guilty of perpetuating the chipset/multiple GPU incompatibility (or non-optimization) myths, by not giving us systematic reviews of X38/48 and 680/790i using both ATI and Nvidia twinned cards.And if some BIOS adjustments or driver updates are becessary to twin Nvidia cards under Intel chipsets, or ATI/AMD cards under Nvidia's, kindly tell and guide us.

I'm not a conspiration theorist, but I think there is more than meets the eye in the present situation.

The apparent paradox of Intel (chipsets) pushing AMD (Crossfire) solutions is just marketing cycle hysteresis from the days when ATI was still an independent canadian company.

But both Intel and AMD resent video card chip manufacturers forcing their way into hard-wired motherboard real estate thru the multiple GPU concept, with attendant slot and chipset modifications. With the demise of Via, Intel and AMD believe they can own the chipsets, as long as the motherboard manufacturers are only assemblers.

For Nvidia, multiple GPU is an easy way to extend the life of a good graphic chip until the next generation comes up, but mostly it provides for a temporary proprietary claim on the motherboard design. 3dfx first tried that years ago in Voodoo days and it worked. It worked again when ATI couldn't follow up fast enough on SLI and had to fall in AMD's arms.

Nvidia gambled that SLI would allow it to impose its own chipset business, either by technical or marketing (SLI endorsment) means. What next ? Special gaming CPU's ? That's a dangerous taunt, although Intel doesn't yet dare buy them, or compete directly with them with their own GPU's, out of anti-trust concerns in Brussels.

Holly - Wednesday, January 30, 2008 - link

Excelent description of memory timing magic. Thumbs up :-)FSBastrd - Tuesday, January 29, 2008 - link

I may have come off a little brash with my first comment. The article is pretty sweet, and I was able to read through it without the pictures, but that doesn't mean I wouldn't like to view them. It's not just this article either. Pictures pretty much never load on this website for me.kjboughton - Wednesday, January 30, 2008 - link

Do you run some type of ad blocker? It may be causing problems by incorrectly blocking images from our servers...FSBastrd - Wednesday, January 30, 2008 - link

I'm basically running a stock version of Firefox, so no. Ironically, the ads are just about the only pictures that do load for me. Also, all of the picture for the AnandTech homepage load for me, it's just the pics in the articles This is the only website that really gives me problems. One last thing, some (rare) pictures do load for me from the articles. All in all, it's quite strange, and I can't figure it out.FSBastrd - Tuesday, January 29, 2008 - link

Am I the only one who can't get pictures to load from this site. It would sure make this article a whole lot easier to follow along.sje123 - Tuesday, January 29, 2008 - link

Excellent review as ever!Quick question with regard to Watercooling blocks for this board. It looks more or less identical to the X38 apart from the different chip in the NB, therefore I'm wondering if you could tell me whether or not you think an ASUS X38 NB block would also fit the ASUS X48 Rampage?

is the NB under the cooler the same size etc and are the mouting screws in the same position as the X38 eg the Maximus?

THe SB and the mofset coolers will be the same as the Maximus.

snarfbot - Sunday, January 27, 2008 - link

alright, pretty exciting results here.at trd of 8 (default) at 400mhz 1:1 cas 4, i got 7687mb/s read, and 64ns latency in everest.

at trd of 6 at the same speed, divider and cas setting i got 8089mb/s read, and 59.8ns latency.

then just for fun i bumped the speed upto 500 and loosened the timings to cas 5, at 5:4, i left the trd at 6. at these settings i got 8640mb/s read, and 57.5 latency.

the latency suprised me, as the trd remained the same, and i actually loosened the cas latency.

anyways pretty good results.

processor is a e2140@3200mhz.

snarfbot - Sunday, January 27, 2008 - link

alright, i have a ga-p35-ds3l. im running the fsb at 400, memory at 1:1 cas 4.i set trd to 6 in the bios. based on the formula, it shouldnt even post.

trd(6) - tcl(4)/n(1) =fsb400(2)/1

2=2

im gonna run through sandra and see what the difference is, if there is any, or perhaps this setting doesnt work correctly on this board.

Fyl - Sunday, January 27, 2008 - link

not to lower the merits of this great article but since I've read it I've been experimenting on my machine different settings and for some of them your formula doesn't seem to stand; here's an example of a stable configuration, no overvoltage to anything:E8500@3.6 (400MHzx9)

P35-DS4 (tRD 7)

2x2G DDR2 800 (400MHz, 5-5-5-12)

based on your formula N = 400:400 = 1 and x = 2

therefore 7-(5/1) > 2/1 => 2 > 2 => false but actually working

am I missing anything?